4.23.2026

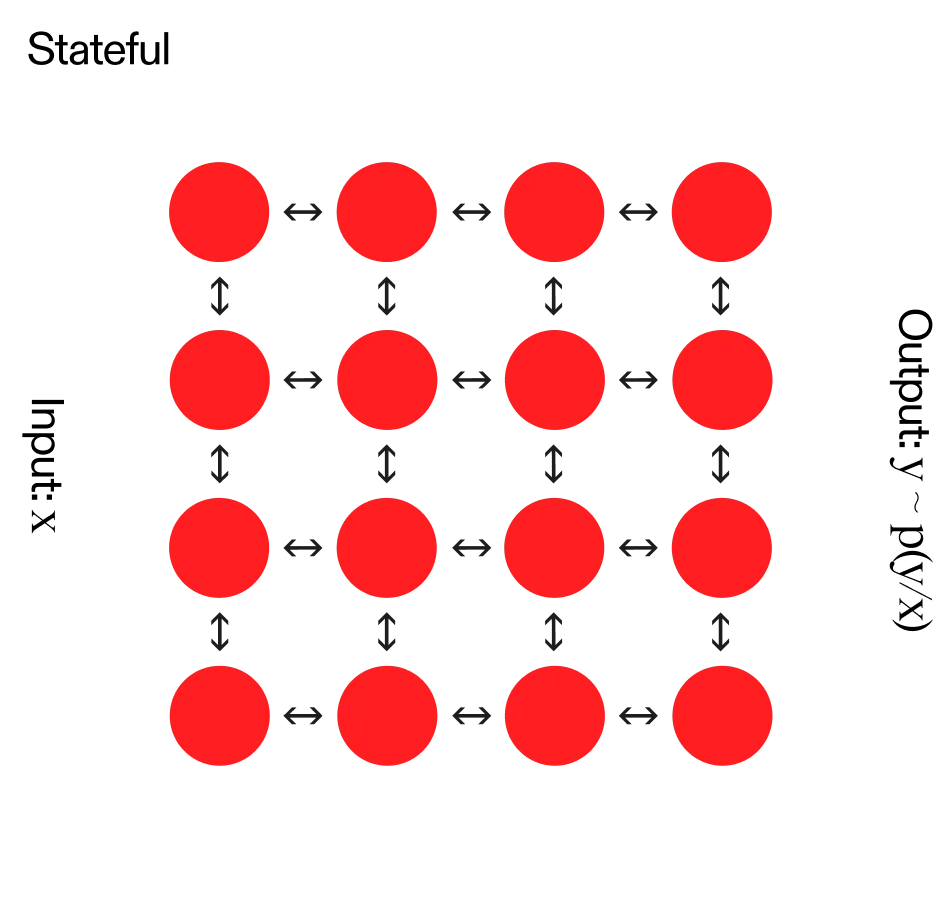

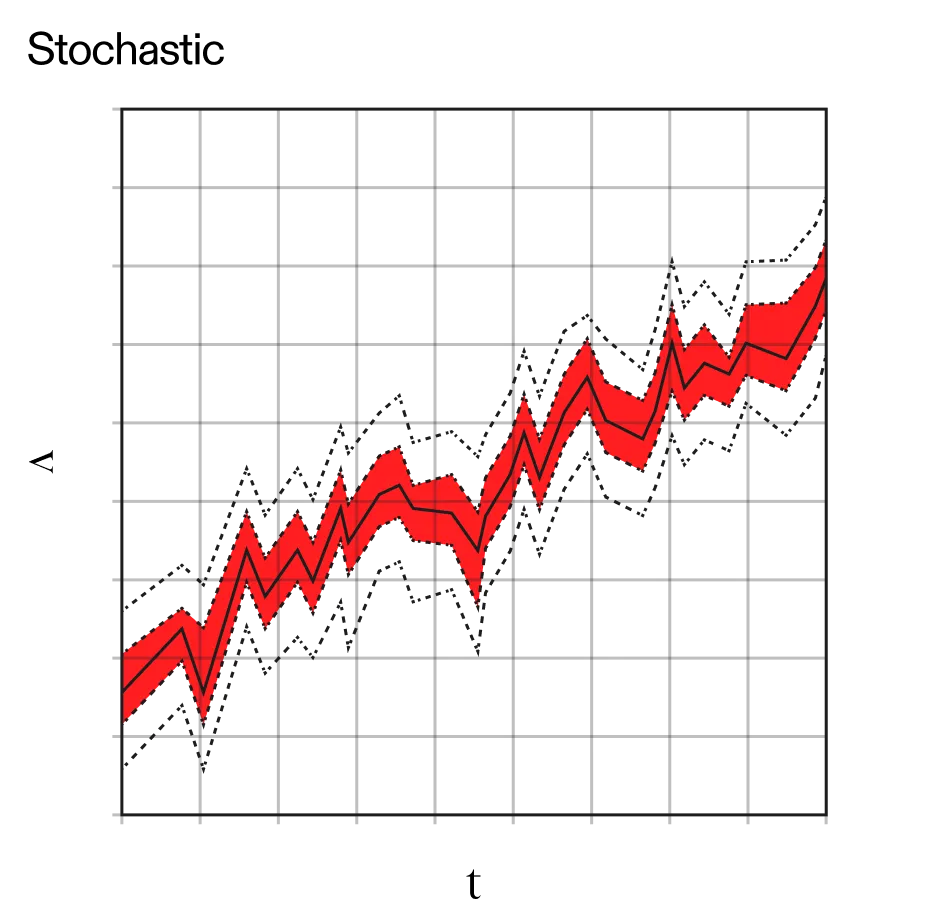

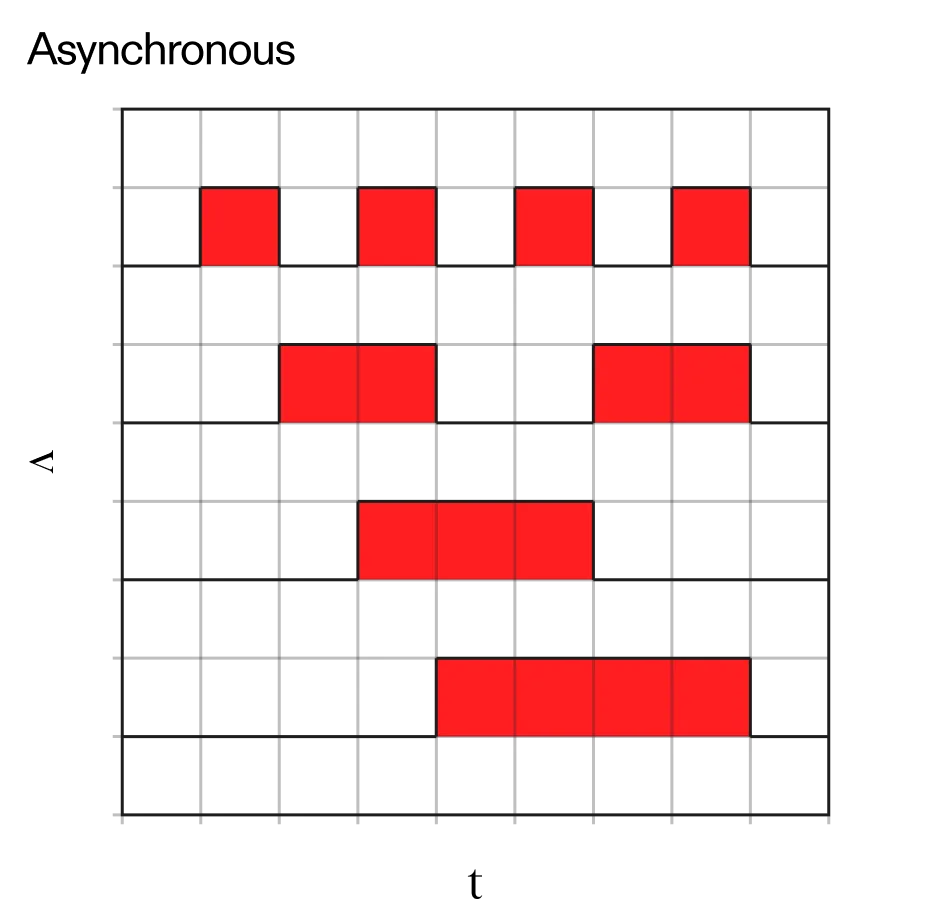

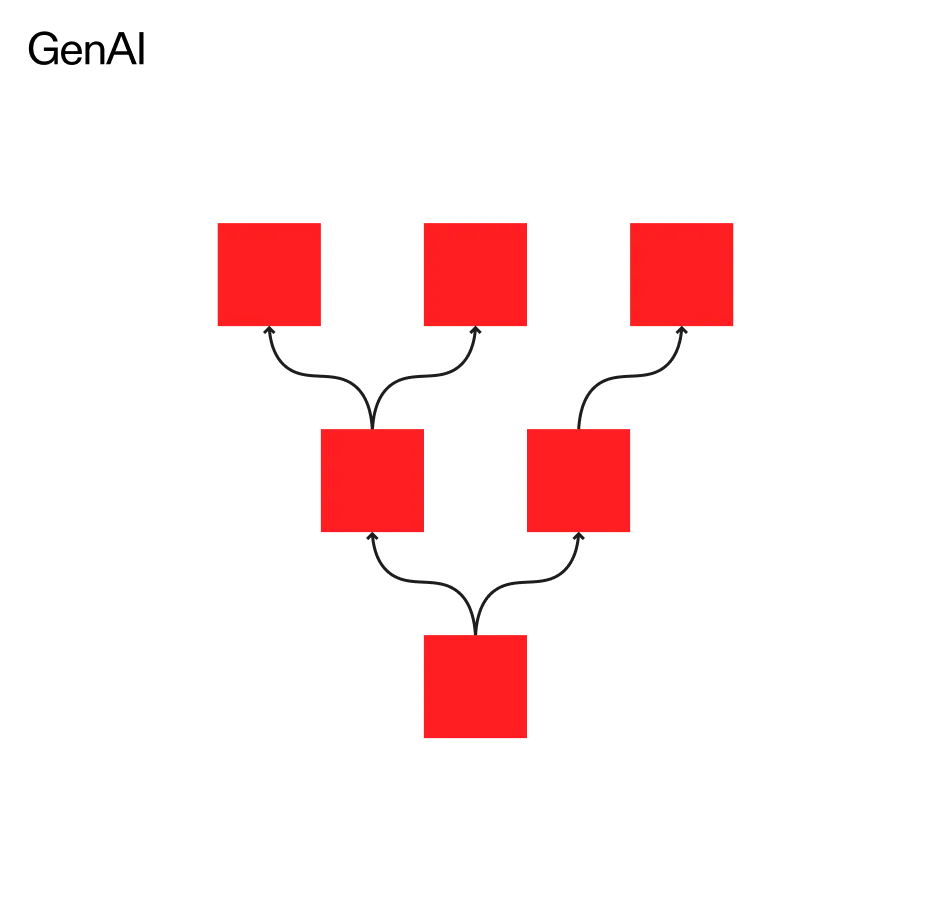

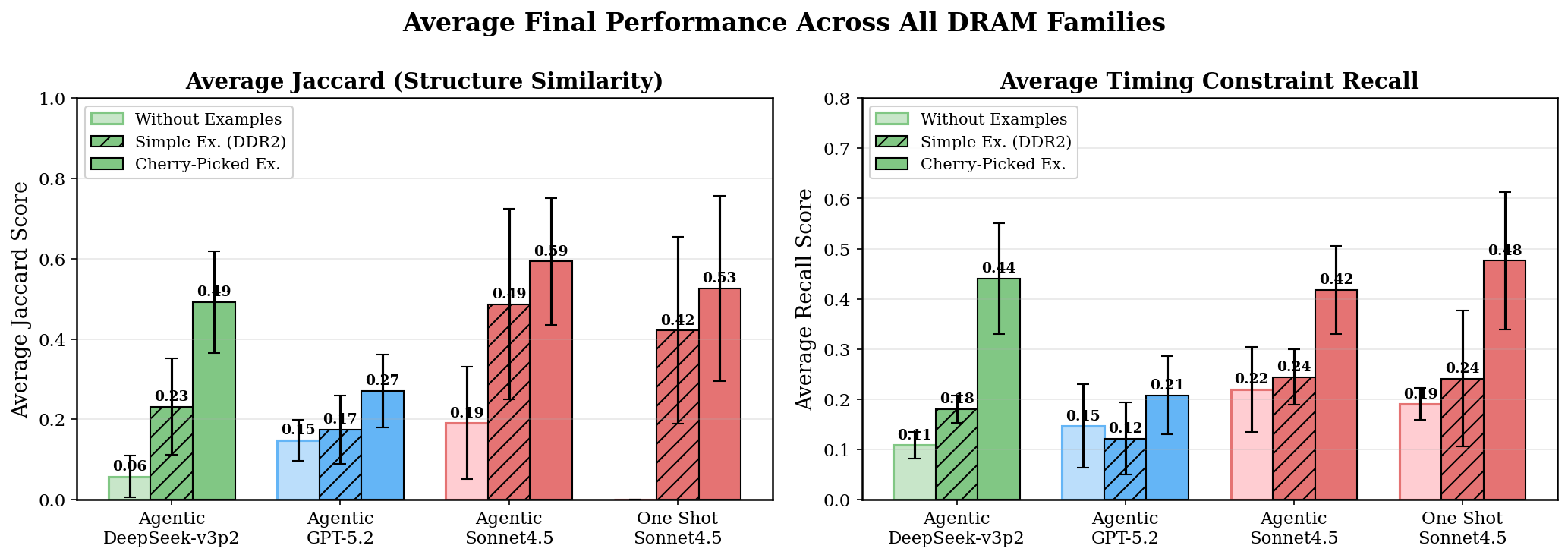

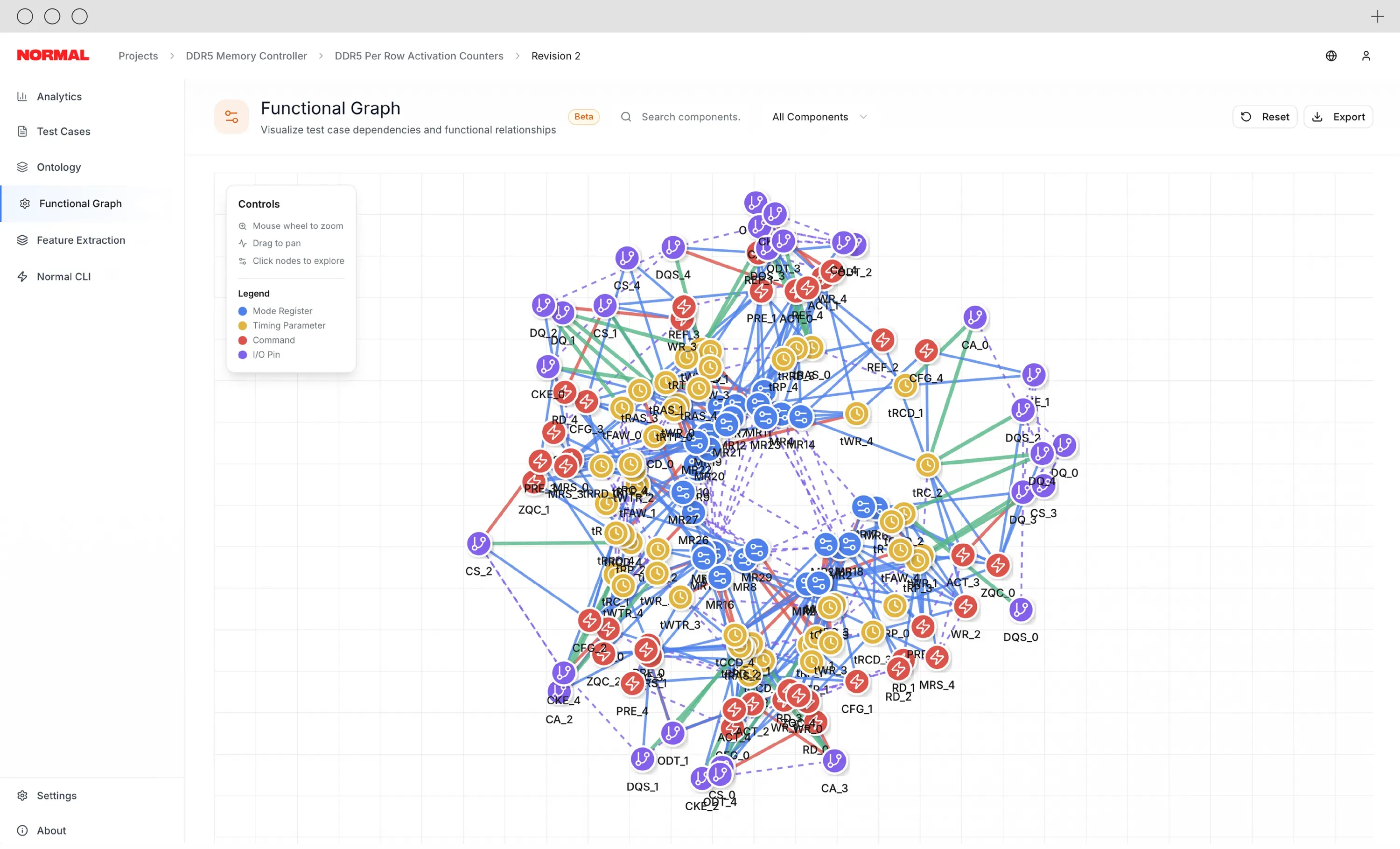

Manual translation of chip standards into verification artifacts is a major bottleneck in chip design. DRAMBench, developed by Normal Computing and Fraunhofer IESE, benchmarks AI systems that turn natural language DRAM specifications into timed Petri net models.

From Specifications to Formal Models: Autoformalizing Memory Chips with DRAMBench

Research

All

%20(1)%201.webp)

%201.webp)

%204.webp)